福建省“十四五”普通高等教育本科规划教材

“十四五”时期国家重点出版物出版专项规划项目

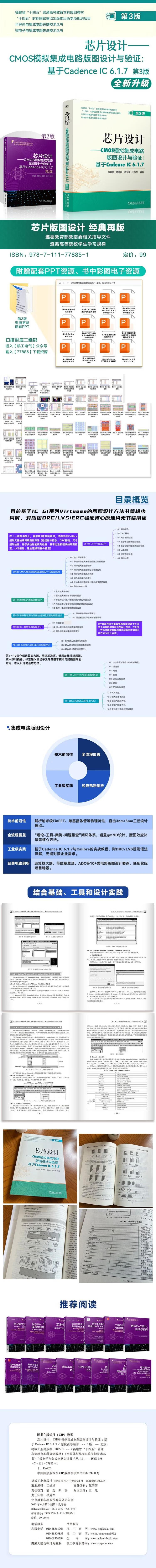

本书聚焦CMOS模拟集成电路版图设计领域,从版图的基本概念、设计方法和EDA工具入手,循序渐进地介绍了CMOS模拟集成电路版图规划、布局、设计到流片的全流程;详尽地介绍了目前主流使用的模拟集成电路版图设计和验证工具——Cadence IC 6.1.7与Siemens EDA Calibre Design Solutions(Calibre);也介绍了Calibre DRC、LVS规则的基本语法,同时展示了运算放大器、带隙基准源、低压差线性稳压器、模—数转换器等典型模拟集成电路版图的设计实例;并结合实例对LVS验证中的典型案例进行了归纳和总结;最后对集成电路设计使用的工艺设计工具包内容及参数化单元建立方法进行了讨论。 本书通过结合基础、工具和设计实践,由浅入深,使读者深刻了解CMOS模拟集成电路版图设计和验证的规则、流程和基本方法,对于高校集成电路学院进行CMOS模拟集成电路学习的本科生、研究生,以及本领域工程师,都会起到有益的帮助。

目前基于IC 61系列Virtuoso的版图设计方法书籍极少。同时,对版图DRC/LVS/ERC验证核心原理尚无书籍阐述。本书在上一版的基础上,将原第5章重新编写,详细分析Calibre规则文件的编写规范和方法(包括基本概念、DRC基础、尺寸规则检查、基于多边形的规则检查、基于边沿和错误的规则检查、LVS基础、建立连接和器件检查);第9章混合信号集成电路版图设计中补充关于隔离IO的概念以及设计方法;并补充一节两步模数转换器概念和版图布局设计。修订30%以上内容。

修订原因:从底层基础和顶层设计实例两方面进行拓展(1)对版图底层规则文件进行详细介绍和分析;(2)对典型的模数转换器和传感器读出电路版图进行分析介绍,扩展知识广度。

本书针对希望从事集成电路版图设计的技术人员以及有一定半导体理论基础的高校学生。①在本书的帮助下,提高相关集成电路设计人员对于版图设计及验证的理论知识水平,并为他们提供典型设计范例的理论和实践经验。②对于不同知识层次,相关专业的大专院校师生都可以从中获取有益的启迪与参考。

.jpg)